Ceretti Federico Veronese Andrea

PROVA A VUOTO M.A.T. TRAMITE ANALIZZATORE DI RETE

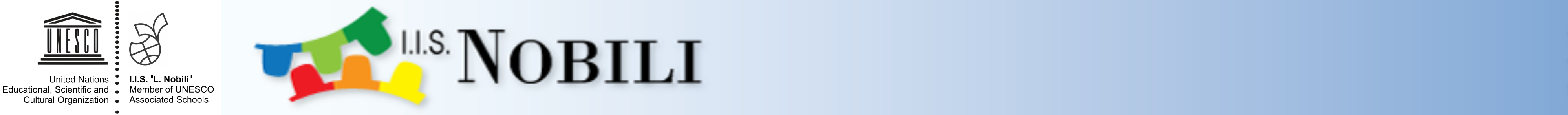

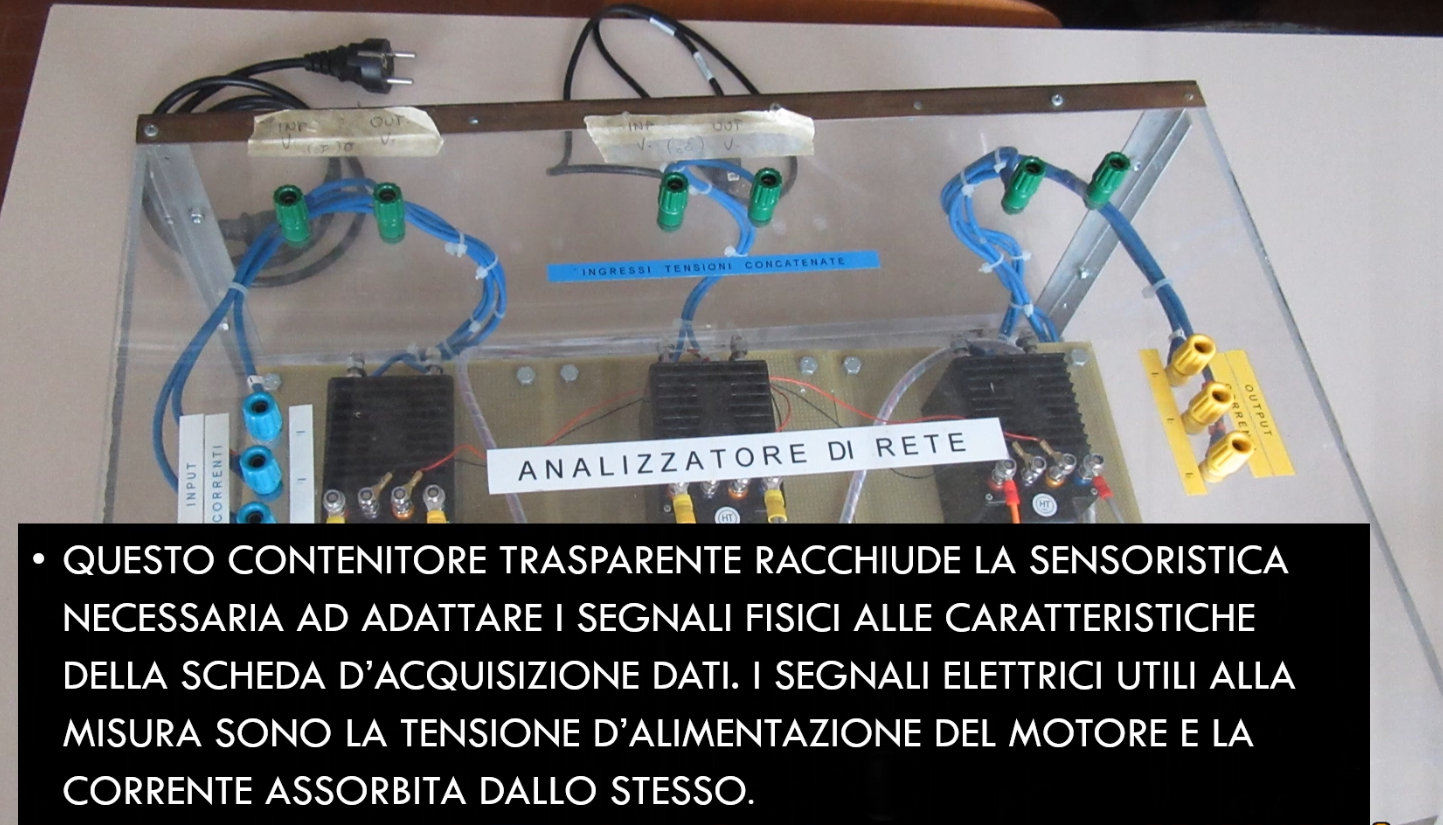

Il progetto prevede l’esecuzione della prova a vuoto sul Motore asincrono Trifase mediante un analizzatore di rete e scheda di acquisizione dati NIUSB6009. L’analizzatore di rete è stato progettato e realizzato da studenti dell’Istituto Tecnico Nobili negli anni precedenti e la gestione dello stesso avviene tramite programma scritto in LabVIEW.

Il sistema di misura acquisisce le tensioni concatenate e le correnti assorbite dal motore in esame, i segnali acquisiti vengono elaborati dal software scritto in LabVIEW al fine di ricavare i parametri significativi tipici della prova.

Obiettivi del progetto sono: lo studio del sistema, l’ottimizzazione del codice LabVIEW, la realizzazione della prova e l’analisi dei risultati. In particolare la scrittura della nuova versione del software è relativa al salvataggio su file dei risultati e all’elaborazione e visualizzazione della separazione delle Perdite nel Ferro a tensione nominale dalle Perdite Meccaniche a velocità nominale.

Studenti coinvolti, classe 5D, indirizzo Elettronica ed Elettrotecnica, articolazione Elettrotecnica: Ceretti Federico, Veronese Andrea

Immagini:

Video del progetto: